【康沃真空網】薄膜沉積是晶圓制造的三大核心步驟之一,薄膜的技術參數直接影響芯片性能。半導體器件的不斷縮小對薄膜沉積工藝提出了更高要求,而ALD技術憑借沉積薄膜厚度的高度可控性、優異的均勻性和三維保形性,在半導體先進制程應用領域彰顯優勢。

由于低溫沉積、薄膜純度以及絕佳覆蓋率等固有優點,ALD(原子層淀積)技術早從21世紀初即開始應用于半導體加工制造。DRAM電容的高k介電質沉積率先采用此技術,但近來ALD在其它半導體工藝領域也已發展出愈來愈廣泛的應用。

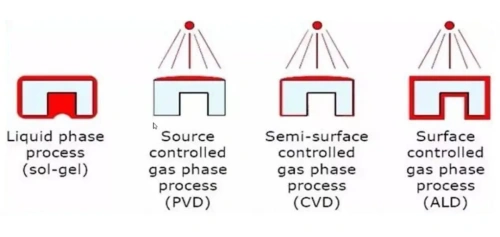

用于薄膜沉積的技術包括物理氣相沉積(PVD)、化學氣相沉積(CVD)和原子層沉積(ALD)。

其中ALD是CVD的變種形式,是一種將物質以單原子膜的形式逐層鍍在基底表面的方法,將襯底依次暴露到兩種活潑的氣相化學前驅物中即可形成ALD化合物材料,襯底在特定時間只暴露到一種前驅物中,暴露時間控制得很短,使襯底上僅僅形成一層所吸附前驅物的亞單原子覆蓋層。可以通過控制沉積周期次數實現薄膜厚度的精準控制。能夠實現納米量級超薄膜的沉積。

目前ALD技術可以細分為TALD、PEALD、SALD等,制備的薄膜類型包括氧化物、氮(碳)化物、金屬與非金屬單質等,涵蓋介電層、導體和半導體。ALD反應的自限制性和窗口溫度較寬的特征,使其生長的薄膜具有很好的臺階覆蓋率、大面積均勻、致密無孔洞且厚度等沉積參數易于精確控制。ALD技術特別適合復雜形貌、高深寬比溝槽表面的薄膜沉積,被廣泛應用于High-K柵介質層、金屬柵、銅擴散阻擋層等半導體先進制程領域。

ALD鍍膜的最大優勢在于臺階的覆蓋性,如下圖所示:

一個原子層沉積周期可以分為如下幾個階段:

1、通入一種前驅體,與基體表面發生吸附或化學反應;

2、惰性氣體沖洗剩余氣體;

3、通入第二種前驅體氣體,與第一層的前驅體生成物進行反應

4、惰性氣體沖洗剩余氣體

ALD技術在半導體制造中的關鍵作用如下:

晶體管柵極介電層(高介電常數)

介電常數是描述一種材料保有電荷的能力,更高的K值,更好地存儲電荷。

高K值材料,相同電容密度下,可以減少漏電流。

金屬柵極

利用金屬代替多晶硅作為器件的柵極材料,同時金屬柵極具有極高的電子密度,可以把極性分子的振動屏蔽掉,提供器件通道內的遷移率,有效解決多晶硅柵極耗盡問題。

金屬代替柵極,金屬沉積在多晶硅的溝槽里,要求沉積工藝具有良好的臺階覆蓋率。

銅互連阻擋層

互連技術常用的工藝主要有Al工藝和Cu工藝,Cu導電性更優良,能夠在低溫下進行沉積,使用更廣泛。Cu最大的缺點是擴散速度很快,容易在電介質內部移動使器件“中毒”,因此鍍銅之前必須首先沉積一層防擴散的阻擋層.ALD技術沉積Cu擴散層,高深寬比下,薄膜仍具有良好的均勻性以及防擴散阻擋特性。

微型電容器

ALD在電容器中應用主要包括100nm以下DAM、和嵌入式DRAM等。存儲器容量擴大,內部電容器數量劇增,單個電容器尺寸進一步減小,電容器內部溝槽的深寬比越來越大,沉積薄膜的有效面積是器件本身的20倍左右。ALD技術可以滿足大面積均勻性,高臺階覆蓋率和對膜厚的精確控制。

ALD在半導體領域的應用。隨著摩爾定律不斷演化,集成電路的特征尺寸及刻蝕溝槽不斷微縮,越來越小的刻蝕溝槽給溝槽及其側壁的鍍膜技術帶來嚴苛的挑戰,傳統PVD及CVD工藝已經無法滿足小線寬下良好的臺階覆蓋要求。ALD技術具有優良的保型性和均勻性以及較高的臺階覆蓋率,開始在半導體產業扮演越來越重要的角色。